- 게이트 레벨 최소화의 방법(수식, 진리표-Kmap, Program)

- Karnaugh Map(K-map)은 variable 2~5, Minterm을 구해서 다 더한다(이 때 2의 지수승으로 묶어서 처리)

- 최소화 원칙(minterm의 합, 중복x, 항 최소화), Prime Implicant, Essential Prime Implicant

- Product of Sum은 Kmap에서 보수를 취해서 구한 다음 다시 보수 취하기

- Don't Care 조건은 어떤 값이든 넣어서 최소화를 이행하면 된다

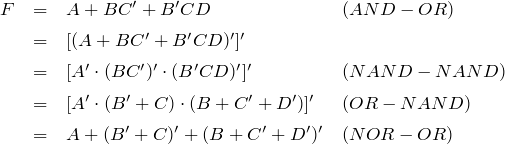

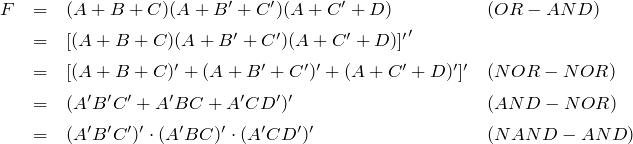

- NAND 게이트와 NOR 게이트로 표현하기

- 2 레벨 게이트 구현(AND-OR, OR-AND을 구해서 보수의 보수 취해가면서 찾아보기)

- XOR 게이트(xy'+x'y), Odd Function, Even Function, 패리티 체크

- HDL(HardWare Description Language), Verilog는 C like

- HDL은 Module로 표현되고 input, output, assign, 게이트(AND,OR,...), timescale(#30) 등을 사용

- HDL은 Test-Bench라는 main module로 실행(wire, reg, initial begin, initial $finish)

2 레벨 게이트 구현

'Archived(CSE) > 논리회로' 카테고리의 다른 글

| Chap 7. 메모리와 프로그래머블 논리 (0) | 2019.06.07 |

|---|---|

| Chap 6. 레지스터와 카운터 (0) | 2019.06.01 |

| Chap 5. 동기 순차논리 (0) | 2019.06.01 |

| Chap 2. 부울 대수와 논리게이트 (0) | 2019.04.14 |

| Chap 1. 디지털 시스템과 2진수 체계 (0) | 2019.04.14 |